3D NANDの性能、信頼性、歩留まりの向上に関する考察

ホワイトペーパー

このホワイトペーパーは、3D NANDの設計と製造における固有の課題とそれを克服するための考察について詳しく述べています。

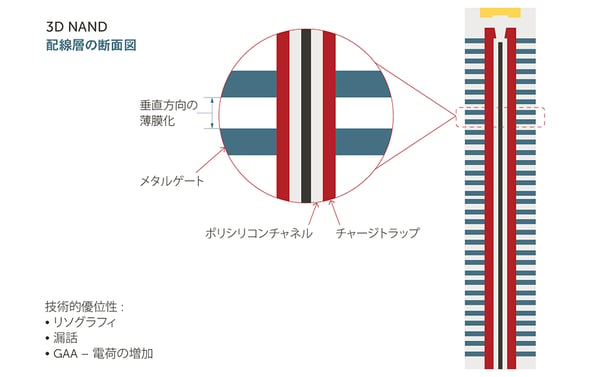

>NANDフラッシュ技術は長年にわたって、世界に不揮発性メモリーに備わった能力を提示してきました。その用途はフラッシュドライブからノートブックPC、スマートフォン、タブレット、ソリッドステート装置のアプリケーションのみならず、今やクラウドストレージに至るまでに拡大しています。長い時間をかけて、その構造は、高まるストレージ容量や微細化のニーズ、信頼性への要求に応えるべく変化し続けていますが、NANDフラッシュ技術は、向上した性能を低電力消費かつ前世代のソリッドステートメモリー技術よりも低減されたビットあたりコストを保証して提供することで、その価値を証明してきました。 当初、NANDフラッシュメモリーメーカーはマルチパターニング技術の採用によって徐々に寸法の微細化を達成することで、メモリー密度の向上とそれに伴うコスト削減を実現してきました。しかし、残念ながら、2D/プラナー型NANDフラッシュメモリーは15 nmのテクノロジーノードでスケーリング(デバイスの微細化) の限界に達してしまいました。これを機に、メーカーは、新しい性能目標を達成しうる画期的な積層ゲートオールアラウンド(Gate-All-Around) 構造のNANDセルの採用を強いられることになりました。現在の3D NAND構造はこのようにして生まれ、それ自体がスケーリング方法の抜本的な転換を示すものとなっています。この技術は、二次元の平面上で水平方向に微細化を図るのではなく、垂直方向(三次元) への積層化を導入しました(図 1a および 1b を参照)。3D NANDは、高密度化とビットあたりコストの削減に大きな期待が持たれています。

あらゆる有望な利点を備える3D NANDですが、プロセスの複雑さ、投資額の破格さに加えて、その製造において特にファブではプロセスコントロール、歩留まり、経済性の面で数々の課題に直面ています。多大な資本投下により、24、32、48 層の3D NANDの製造プロセスは競争力の高いビットあたりコストを実現すべく開発されました。